AMD Zen5 and Zen6 details leak out

A new leak has just been shared by Moore’s Law is Dead channel.

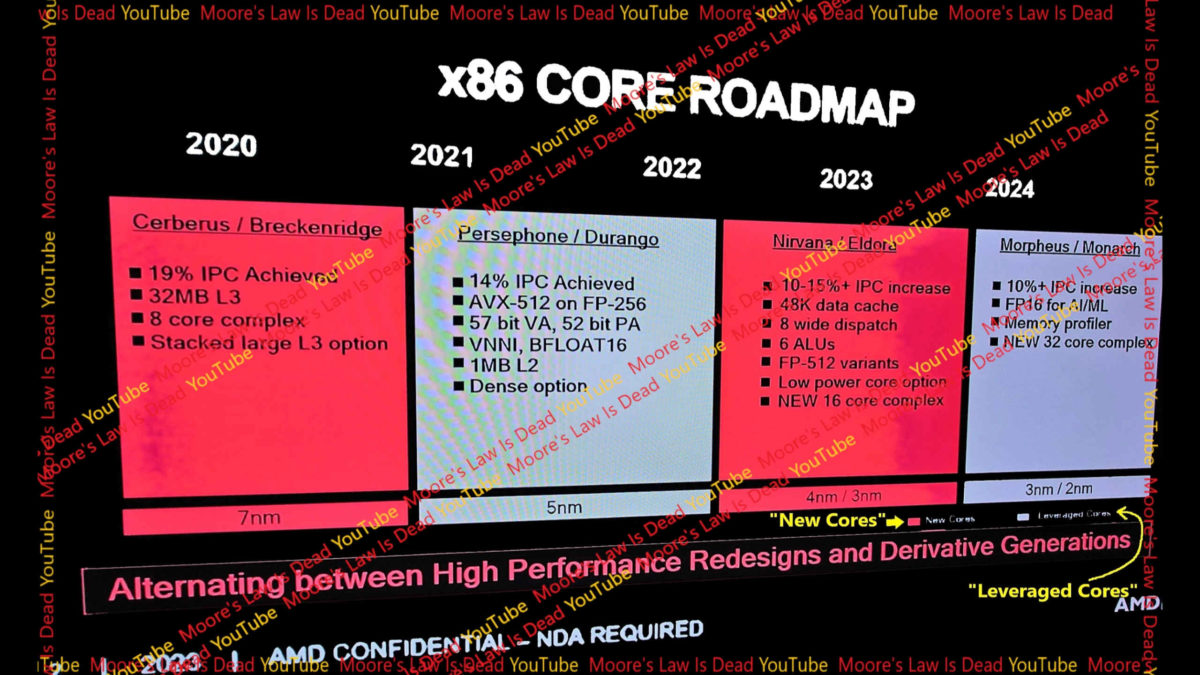

AMD x86 Core Roadmap, Source: Moore’s Law is Dead

The YouTuber has shared two slides extracted from an AMD internal presentation, originally not intended for public consumption. These slides furnish an update on the progress and strategies pertaining to the forthcoming Zen architectures of the next generation, revealing some fundamental details like anticipated IPC improvements, supported features, and core counts.

The roadmap appears to have undergone a minor temporal adjustment. However, it is crucial to bear in mind that these microarchitectures encompass a wide range of products, encompassing both data center and consumer-oriented series. As a result, the release timelines may not exclusively mirror AMD’s intentions for Ryzen 8000 and beyond, but also encompass considerations for EPYC products.

Nirvana Zen5 (1H 2024)

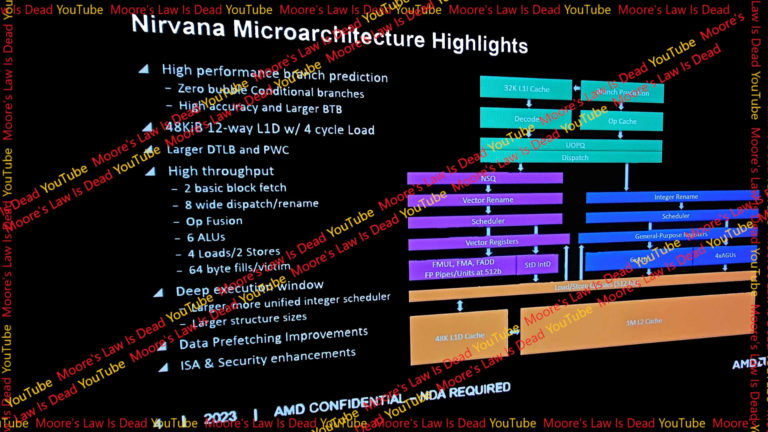

The new 4nm/3nm microarchitectures outlined include Nirvana (Zen5) which is intended for Ryzen 8000 series. According to the slide, it is expected to have a 10 to 15% IPC increase. The IPC may still increase, as the presentation only shows a goal that has yet not been verified by retail silicon. Furthermore, the slide lists 48K data cache, 8 wide dispatches, 6 ALUs, FP-512 variants and a new low power core option.

More interestingly, it is said to offer a 16-core complex. The latter is likely an option using exclusively Zen5c variants. As a reminder, Strix Point APU will use both sub architectures within one die. In other words, gamers on the AM5 platform should expect up to 16-core Zen5 designs or 32-core Zen5c, or a mix of both, should AMD go that route (such as 8x Zen5 + 16x Zen5c).

AMD Nirvana (Zen5), Source: Moore’s Law is Dead

Morpheus Zen6 (2H 2025)

The Morpheus is the microarchitecture codename for Zen6. It is now expected to use 3nm and 2nm process technology, and AMD has a goal to reach a 10% IPC increase over Nirvana. AMD is planning to introduce FP16 instruction for AI/ML algorithms acceleration, and a new memory profiler. In terms of core complex, AMD is increasing the core count to 32, which again should refer to Zen6c, not Zen6.

The Zen6 microarchitecture is said to offer a similar chip layout redesign to Zen2 with new packaging techniques, claims MLID. While it is not confirmed, it is mentioned that for Zen6 AMD might be stacking CCDs on top of the IOD (input/output interface die). This would be a major shift in AMD’s disaggregated chiplet design approach to die stacking. What remains to be confirmed is whether Zen6 is going to use the AM5 socket.

Source: